# **Chapter #2: Two-Level Combinational Logic**

Contemporary Logic Design

Randy H. Katz University of California, Berkeley

May 1993

■ © R.H. Katz Transparency No. 2-1

#### Motivation

Contemporary Logic Design Two-Level Logic

Further Amplification on the Concepts of Chapter #1:

Rapid prototyping technology

Use of computer aided design tools: espresso

• Design Techniques that Spanning Multiple Technologies

Transistor-Transistor Logic (TTL)

Complementary Metal on Oxide Silicon (CMOS)

• Multiple Design Representations

**Truth Tables**

Static gate descriptions

Dynamic waveform descriptions

© R.H. Katz Transparency No. 2-2

#### **Chapter Overview**

Contemporary Logic Design Two-Level Logic

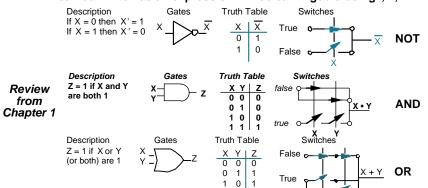

Logic Functions and Switches

Not, AND, OR, NAND, NOR, XOR, XNOR

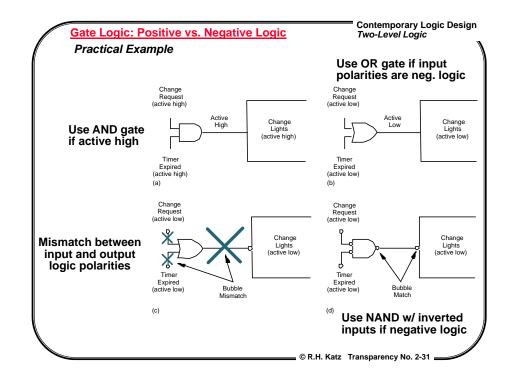

• Gate Logic

Laws and Theorems of Boolean Algebra

**Two Level Canonical Forms**

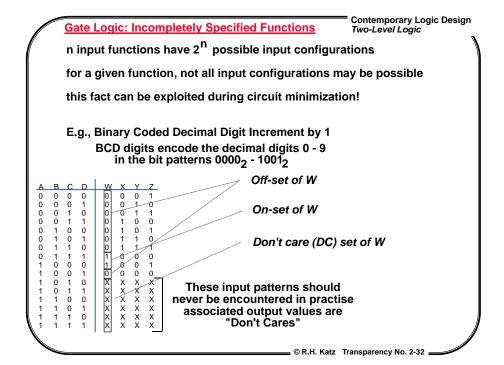

**Incompletely Specified Functions**

• Two Level Simplification

**Boolean Cubes**

**Karnaugh Maps**

**Quine-McClusky Method**

**Espresso Methos**

Logic Functions: Boolean Algebra

Contemporary Logic Design Two-Level Logic

Algebraic structure consisting of:

set of elements B

binary operations {+, •}

unary operation {'}

such that the following axioms hold:

- 1. B contains at least two elements, a, b, such that a b

- 2. Closure a,b in B,

- (i) a + b in B

- (ii) a b in B

- 3. Commutative Laws: a,b in B,

- (i) a + b = b + a

- (ii) a b = b a

- 4. Identities: 0, 1 in B

- (i) a + 0 = a

- (ii) a 1 = a

5. Distributive Laws:

(i)  $a + (b \cdot c) = (a + b) \cdot (a + c)$

(ii)  $a \cdot (b + c) = a \cdot b + a \cdot c$

6. Complement:

(i) a + a' = 1

(iii)  $\mathbf{a} \cdot \mathbf{a}' = \mathbf{0}$

# Logic Functions: Boolean Algebra

Contemporary Logic Design Two-Level Logic

$B = \{0,1\}, + = OR, \bullet = AND, ' = NOT$  is a Boolean Algebra

must verify that the axioms hold:

E.g., Commutative Law:

Theorem: any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using ', +, •

1 1

Contemporary Logic Design Two-Level Logic

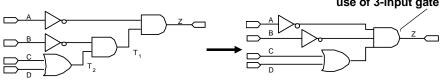

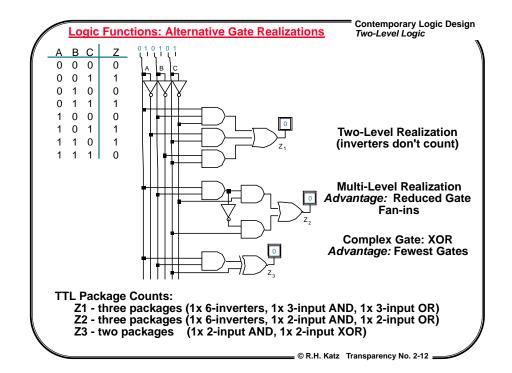

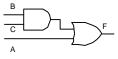

More than one way to map an expression to gates

E.g.,

$$Z = A' \cdot B' \cdot (C + D) = (A' \cdot (B' \cdot (C + D)))$$

use of 3-input gate

Literal: each appearance of a variable or its complement in an expression E.g., Z = AB'C + A'B + A'BC' + B'C

3 variables, 10 literals

© R.H. Katz Transparency No. 2-6

# Logic Functions: NAND, NOR, XOR, XNOR

Contemporary Logic Design Two-Level Logic

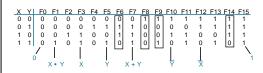

16 functions of two variables:

Review

from

X, X', Y, Y', X•Y, X+Y, 0, 1 only half of the possible functions

© R.H. Katz Transparency No. 2-5

© R.H. Katz Transparency No. 2-7

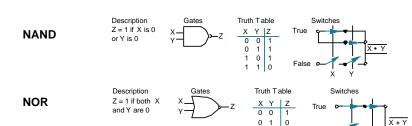

1 0 0 1 1 0 Logic Functions: NAND, NOR Implementation

Contemporary Logic Design Two-Level Logic

NAND, NOR gates far outnumber AND, OR in typical designs easier to construct in the underlying transistor technologies

Any Boolean expression can be implemented by NAND, NOR, NOT gates

In fact, NOT is superfluous

(NOT = NAND or NOR with both inputs tied together)

| X | Υ | X NOR Y | _X | Υ | X NAND Y |

|---|---|---------|----|---|----------|

| 0 | 0 | 1       | 0  | 0 | 1        |

| 1 | 1 | 0       | 1  | 1 | 0        |

Contemporary Logic Design Two-Level Logic

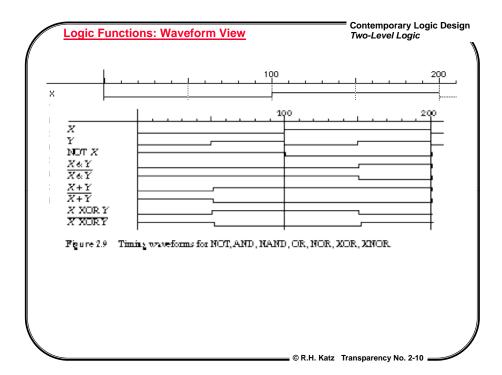

XOR: X or Y but not both ("inequality", "difference")

XNOR: X and Y are the same ("equality", "coincidence")

Description Z = 1 if X has a different

Description

Z = 1 if X has the same value as Y

value than Y

**>**\_-

Gates X Y

Truth Table

X Y Z 0 0 0 0 1 1 1 0 1 1 1 0 Truth Table

X Y Z

0 0 1

0 1 0

1 0

0 0

1 1

(a) XOR

(b) XNOR

$X \oplus Y = X Y' + X' Y$

$\overline{X \oplus Y} = XY + X'Y'$

© R.H. Katz Transparency No. 2-9

#### **Logic Functions: Rationale for Simplification**

Contemporary Logic Design Two-Level Logic

Logic Minimization: reduce complexity of the gate level implementation

- reduce number of literals (gate inputs)

- · reduce number of gates

- reduce number of levels of gates

fewer inputs implies faster gates in some technologies

fan-ins (number of gate inputs) are limited in some technologies

fewer levels of gates implies reduced signal propagation delays

minimum delay configuration typically requires more gates

number of gates (or gate packages) influences manufacturing costs

Traditional methods: reduce delay at expense of adding gates

New methods:

trade off between increased circuit delay and reduced gate count

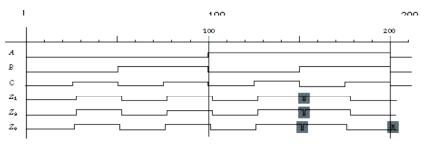

Logic Functions: Waveform Verification

Contemporary Logic Design Two-Level Logic

Figure 2.11 Waveform behavior of three implementations of the traft table of Figure 2.9(a).

Under the same input stimuli, the three alternative implementations have essentially the same waveform behavior.

Slight variations due to differences in number of gate levels

The three implementations are equivalent

© R.H. Katz Transparency No. 2-13

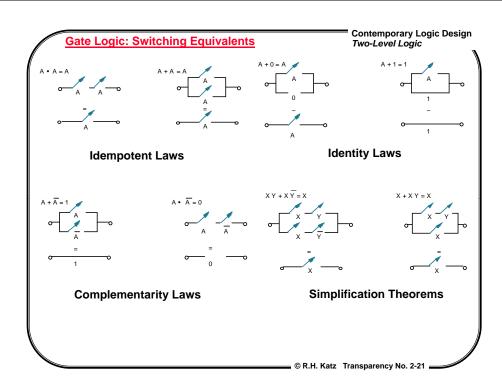

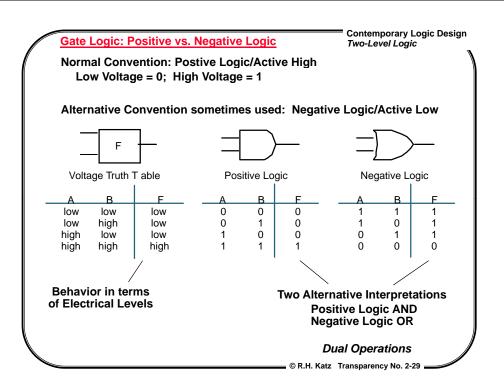

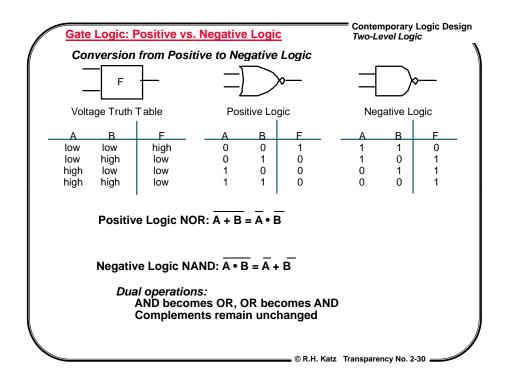

#### Gate Logic: Laws of Boolean Algebra

Contemporary Logic Design Two-Level Logic

Duality: a dual of a Boolean expression is derived by replacing AND operations by ORs, OR operations by ANDs, constant 0s by 1s, and 1s by 0s (literals are left unchanged).

Any statement that is true for an expression is also true for its dual!

Useful Laws/Theorems of Boolean Algebra:

Operations with 0 and 1:

1.

$$X + 0 = X$$

2.

$$X + 1 = 1$$

3.

$$X + X = X$$

3D.

$$X \cdot X = X$$

Involution Law:

4.

$$(X')' = X$$

Laws of Complementarity:

5D.

$$X \cdot X' = 0$$

6D.

$$X \cdot Y = Y \cdot X$$

© R.H. Katz Transparency No. 2-1

#### Gate Logic: Laws of Boolean Algebra (cont)

Contemporary Logic Design Two-Level Logic

#### Associative Laws:

7.

$$(X + Y) + Z = X + (Y + Z)$$

7D.

$$(X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)$$

=  $X \cdot Y \cdot Z$

#### Distributive Laws:

8.

$$X \cdot (Y + Z) = (X \cdot Y) + (X \cdot Z)$$

8D.

$$X + (Y \cdot Z) = (X + Y) \cdot (X + Z)$$

#### Simplification Theorems:

9.

$$X \cdot Y + X \cdot Y' = X$$

9D.

$$(X + Y) \cdot (X + Y') = X$$

10D.

$$X \cdot (X + Y) = X$$

11D.  $(X \cdot Y') + Y = X + Y$

# DeMorgan's Law:

Duality:

14.

$$(X + Y + Z + ...)^D = X \cdot Y \cdot Z \cdot ...$$

14D.  $(X \cdot FY \cdot Z \cdot ...)^D = X + Y + Z + ...$

15.

$$\{F(X1,X2,...,Xn,0,1,+,\bullet)\}^D = \{F(X1,X2,...,Xn,1,0,\bullet,+)\}$$

# Theorems for Multiplying and Factoring:

16.

$$(X + Y) \cdot (X' + Z) = X \cdot Z + X' \cdot Y$$

16D.  $X \cdot Y + X' \cdot Z = (X + Z) \cdot (X' + Y)$

#### Consensus Theorem:

17.

$$(X \cdot Y) + (Y \cdot Z) + (X' \cdot Z) = X \cdot Y + X' \cdot Z$$

17D.

$$(X + Y) \cdot (Y + Z) \cdot (X' + Z) = (X + Y) \cdot (X' + Z)$$

## Gate Logic: Laws of Boolean Algebra

Contemporary Logic Design Two-Level Logic

# Proving theorems via axioms of Boolean Algebra:

E.g., prove the theorem:  $X \cdot Y + X \cdot Y' = X$

E.g., prove the theorem:  $X + X \cdot Y = X$

#### Gate Logic: Laws of Boolean Algebra

Contemporary Logic Design Two-Level Logic

Proving theorems via axioms of Boolean Algebra:

E.g., prove the theorem:  $X \cdot Y + X \cdot Y' = X$

distributive law (8)  $X \cdot Y + X \cdot Y' = X \cdot (Y + Y')$

complementary law (5)  $X \cdot (Y + Y') = X \cdot (1)$

identity (1D)  $X \cdot (1) = X$

E.g., prove the theorem:  $X + X \cdot Y = X$

identity (1D)  $X + X \cdot Y = X \cdot 1 + X \cdot Y$

distributive law (8)  $X \cdot 1 + X \cdot Y = X \cdot (1 + Y)$

identity (2)  $X \cdot (1 + Y) = X \cdot (1)$

identity (1)  $X \cdot (1) = X$

■ © R.H. Katz Transparency No. 2-17

#### **Gate Logic: Laws of Boolean Algebra**

Contemporary Logic Design

Two-Level Logic

DeMorgan's Law

$$(X \cdot Y)' = X' + Y'$$

NAND is equivalent to OR with inputs complemented  $\begin{bmatrix} X & Y & \overline{X} & \overline{Y} & \overline{X} \cdot \overline{Y} & \overline{X} \cdot \overline{Y} & \overline{X} + \overline{Y} \\ \hline 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 0 \end{bmatrix}$

DeMorgan's Law can be used to convert AND/OR expressions to OR/AND expressions

Example:

$$Z' = (A + B + C') \cdot (A + B' + C') \cdot (A' + B + C') \cdot (A' + B' + C)$$

■ © R.H. Katz Transparency No. 2-18

#### **Gate Logic: Laws of Boolean Algebra**

Contemporary Logic Design Two-Level Logic

Apply the laws and theorems to simplify Boolean equations

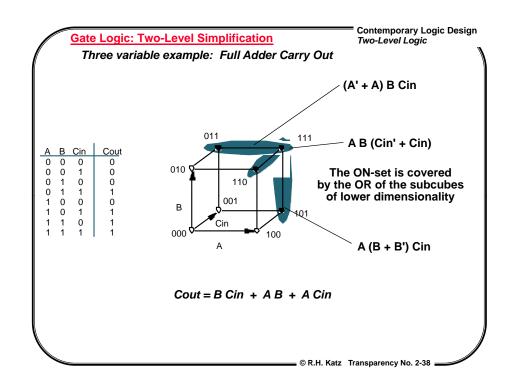

Example: full adder's carry out function

Cout = A' B Cin + A B' Cin + A B Cin' + A B Cin

#### Gate Logic: Laws of Boolean Algebra

Contemporary Logic Design Two-Level Logic

Apply the laws and theorems to simplify Boolean equations

Example: full adder's carry out function

identity

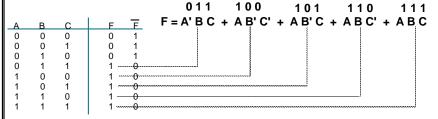

# Gate Logic: 2-Level Canonical Forms

Contemporary Logic Design Two-Level Logic

Truth table is the unique signature of a Boolean function

Many alternative expressions (and gate realizations) may have the same truth table

Canonical form: standard form for a Boolean expression provides a unique algebraic signature

#### Sum of Products Form

also known as disjunctive normal form, minterm expansion

F' = A' B' C' + A' B' C + A' B C'

© R.H. Katz Transparency No. 2-22

#### Gate Logic: Two Level Canonical Forms

Contemporary Logic Design Two-Level Logic

#### Sum of Products

| Α | В | С | Minterms                                       |

|---|---|---|------------------------------------------------|

| 0 | 0 | 0 | $\overline{A} \overline{B} \overline{C} = m_0$ |

| 0 | 0 | 1 | $\overline{A}\overline{B}C = m_1$              |

| 0 | 1 | 0 | $\overline{A} B \overline{C} = m_2$            |

| 0 | 1 | 1 | $\overline{A} B C = m_3$                       |

| 1 | 0 | 0 | $A \overline{B} \overline{C} = m_4$            |

| 1 | 0 | 1 | $A \overline{B} \underline{C} = m_5$           |

| 1 | 1 | 0 | $AB\overline{C} = m_6$                         |

| 1 | 1 | 1 | A B C = m-                                     |

#### **Shorthand Notation for** Minterms of 3 Variables

2-Level AND/OR Realization

#### product term / minterm:

ANDed product of literals in which each variable appears exactly once, in true or complemented form (but not both!)

#### F in canonical form:

$$F(A,B,C) = \Sigma m(3,4,5,6,7)$$

= m3 + m4 + m5 + m6 + m7

= A' B C + A B' C' + A B' C

+ A B C' + A B C

#### canonical form/minimal form

$$F = A B' (C + C') + A' B C + A B (C' + C)$$

$$= AB' + A'BC + AB$$

$$= A (B' + B) + A' B C$$

$$= A + A'BC$$

$$=A + BC$$

$$F = (A + B C)' = A' (B' + C') = A' B' + A' C'$$

© R.H. Katz Transparency No. 2-23

#### Gate Logic: 2 Level Canonical Forms

Contemporary Logic Design Two-Level Logic

# Product of Sums / Conjunctive Normal Form / Maxterm Expansion

| Α | В | С | Maxterms                                           |

|---|---|---|----------------------------------------------------|

| 0 | 0 | 0 | $A + B + C = M_0$                                  |

| 0 | 0 | 1 | $A + B + C = M_1$                                  |

| 0 | 1 | 0 | $A + B + C = M_2$                                  |

| 0 | 1 | 1 | <u>A</u> + B + C = $M_3$                           |

| 1 | 0 | 0 | $\underline{A} + B + \underline{C} = M_4$          |

| 1 | 0 | 1 | $\overline{A} + B + \overline{C} = M_5$            |

| 1 | 1 | 0 | $\overline{A} + \overline{B} + C = M_6$            |

| 1 | 1 | 1 | $\overline{A} + \overline{B} + \overline{C} = M_7$ |

#### Maxterm:

ORed sum of literals in which each variable appears exactly once in either true or complemented form, but not both!

#### Maxterm form:

Find truth table rows where F is 0 0 in input column implies true literal 1 in input column implies complemented literal

**Maxterm Shorthand Notation** for a Function of Three Variables

$$F(A,B,C) = \Pi M(0,1,2)$$

= (A + B + C) (A + B + C') (A + B' + C)

$$F'(A,B,C) = \Pi M(3,4,5,6,7)$$

$$= (A + B' + C') (A' + B + C) (A' + B + C') (A' + B' + C) (A' + B' + C')$$

#### **Gate Logic: Two Level Canonical Forms**

Contemporary Logic Design Two-Level Logic

Sum of Products, Products of Sums, and DeMorgan's Law

F' = A' B' C' + A' B' C + A' B C'

Apply DeMorgan's Law to obtain F:

$$(F')' = (A' B' C' + A' B' C + A' B C')'$$

$$F = (A + B + C) (A + B + C') (A + B' + C)$$

$$F' = (A + B' + C')(A' + B + C)(A' + B + C')(A' + B' + C)(A' + B' + C')$$

Apply DeMorgan's Law to obtain F:

$$(F')' = \{(A + B' + C') (A' + B + C) (A' + B + C') (A' + B' + C) (A' + B' + C')\}'$$

■ © R.H. Katz Transparency No. 2-25

# Gate Logic: Two-Level Canonical Forms Four Alternative Implementations of F: Canonical Sum of Products Minimized Sum of Products Canonical Products of Sums Minimized Products of Sums

# Gate Logic: Two-Level Canonical Forms Waveform Verification of the Four Alternatives Eight Unique Combinations of Three Inputs Except for timing glitches, output waveforms of the four implementations are essentially identical

#### **Gate Logic: Two-Level Canonical Forms**

Contemporary Logic Design

#### Mapping Between Forms

Minterm to Maxterm conversion:

rewrite minterm shorthand using maxterm shorthand

replace minterm indices with the indices not already used

E.g.,

$$F(A,B,C) = \Sigma m(3,4,5,6,7) = \Pi M(0,1,2)$$

2. Maxterm to Minterm conversion:

rewrite maxterm shorthand using minterm shorthand replace maxterm indices with the indices not already used

E.g.,

$$F(A,B,C) = \prod M(0,1,2) = \sum m(3,4,5,6,7)$$

Minterm expansion of F to Minterm expansion of F': in minterm shorthand form, list the indices not already used in F

E.g.,

$$F(A,B,C) = \Sigma m(3,4,5,6,7)$$

$\longrightarrow$   $F'(A,B,C) = \Sigma m(0,1,2)$

=  $\Pi M(0,1,2)$  =  $\Pi M(3,4,5,6,7)$

Minterm expansion of F to Maxterm expansion of F': rewrite in Maxterm form, using the same indices as F

E.g.,

$$F(A,B,C) = \Sigma m(3,4,5,6,7)$$

$\longrightarrow$   $F'(A,B,C) = \Pi M(3,4,5,6,7)$   $\longrightarrow$   $= \Sigma m(0,1,2)$   $\longrightarrow$   $\bigcirc$  R.H. Katz Transparency No. 2-28

#### **Gate Logic: Incompletely Specified Functions**

Contemporary Logic Design Two-Level Logic

Don't Cares and Canonical Forms

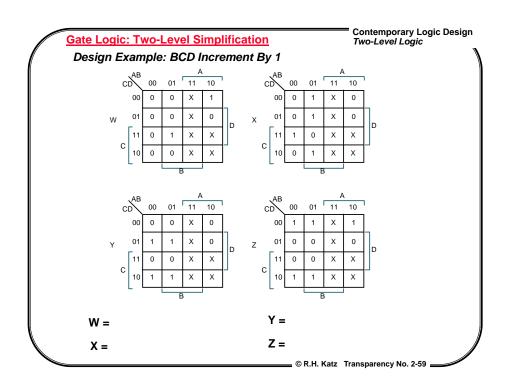

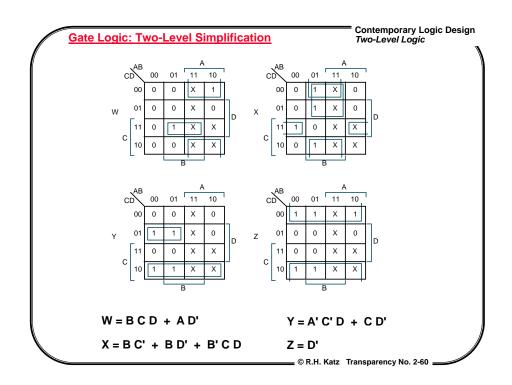

Canonical Representations of the BCD Increment by 1 Function:

$$Z = m0 + m2 + m4 + m6 + m8 + d10 + d11 + d12 + d13 + d14 + d15$$

$$Z = \Sigma m(0, 2, 4, 6, 8) + d(10, 11, 12, 13, 14, 15)$$

$$Z = \Pi M(1, 3, 5, 7, 9) \cdot D(10, 11, 12, 13, 14, 15)$$

© R.H. Katz Transparency No. 2-33

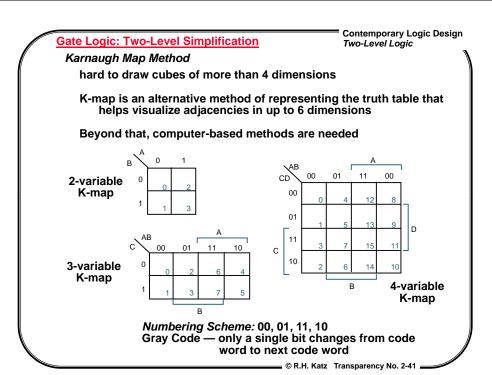

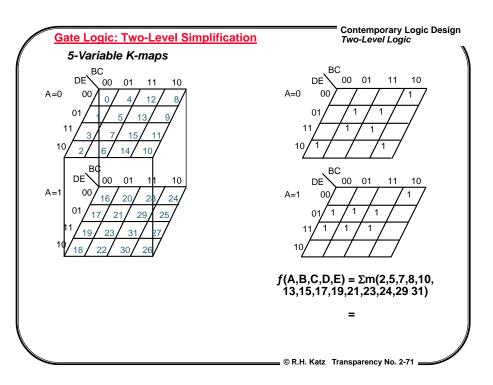

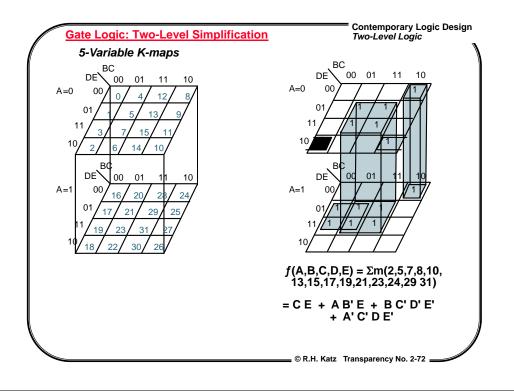

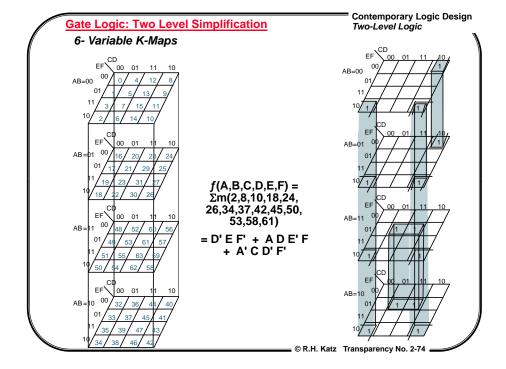

#### Gate Logic: Two-Level Simplification

Contemporary Logic Design Two-Level Logic

Algebraic Simplification:

not an algorithm/systematic procedure

how do you know when the minimum realization has been found?

#### Computer-Aided Tools:

precise solutions require very long computation times, especially for functions with many inputs (>10)

heuristic methods employed —

"educated guesses" to reduce the amount of computation

good solutions not best solutions

#### Still Relevant to Learn Hand Methods:

insights into how the CAD programs work, and their strengths and weaknesses

ability to check the results, at least on small examples

don't have computer terminals during exams

■ © R.H. Katz Transparency No. 2-34

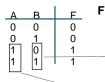

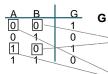

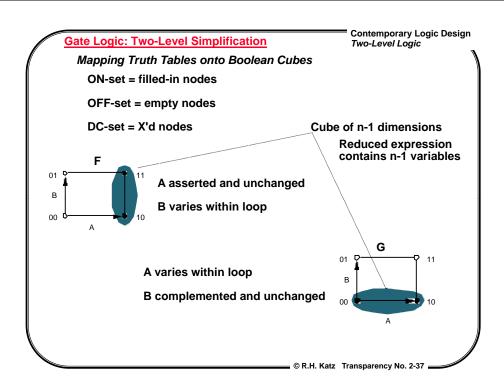

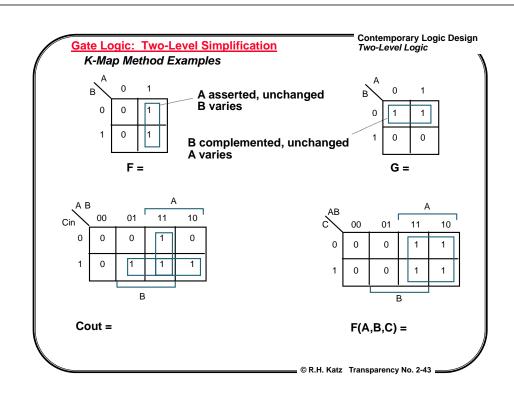

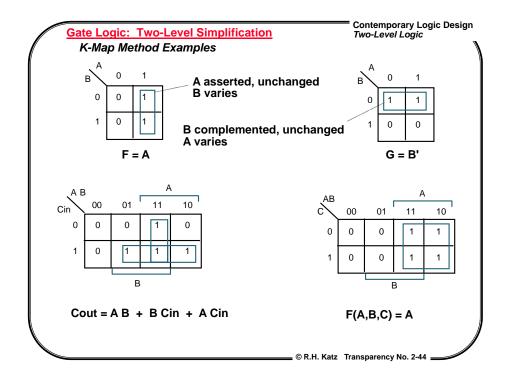

#### Gate Logic: Two-Level Simplification

Contemporary Logic Design Two-Level Logic

# Key Tool: The Uniting Theorem — A (B' + B) = A

F = A B' + A B = A (B' + B) = A

B's values change within the on-set rows

B is eliminated, A remains

A's values don't change within the on-set rows

G = A' B' + A B' = (A' + A) B' = B'

B's values stay the same within the on-set rows

A is eliminated, B remains

A's values change within the on-set rows

#### **Essence of Simplification:**

find two element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

■ © R.H. Katz Transparency No. 2-35

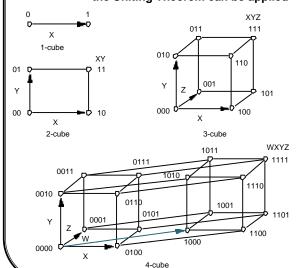

#### **Gate Logic: Two-Level Simplification**

#### **Boolean Cubes**

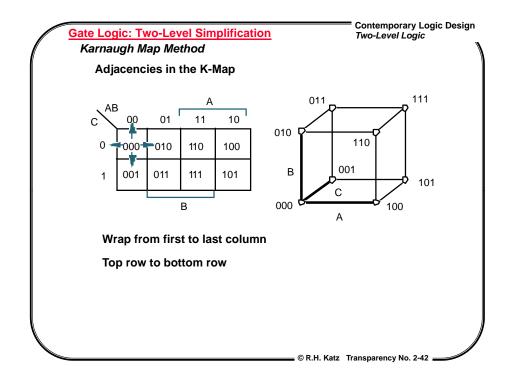

Visual technique for identifying when the Uniting Theorem can be applied

Contemporary Logic Design

Two-Level Logic

Just another way to represent the truth table

n input variables = n dimensional "cube"

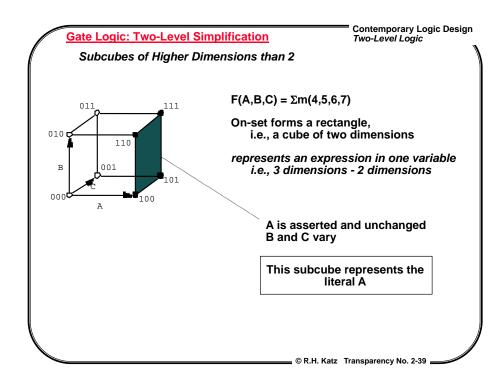

**Gate Logic: Two-Level Simplification**

Contemporary Logic Design

In a 3-cube:

a 0-cube, i.e., a single node, yields a term in three literals

a 1-cube, i.e., a line of two nodes, yields a term in two literals

a 2-cube, i.e., a plane of four nodes, yields a term in one literal

a 3-cube, i.e., a cube of eight nodes, yields a constant term "1"

In general,

an m-subcube within an n-cube (m < n) yields a term with n - m literals

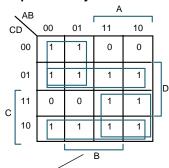

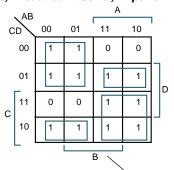

#### Gate Logic: Two-Level Simplification

Contemporary Logic Design

Two-Level Logic

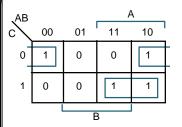

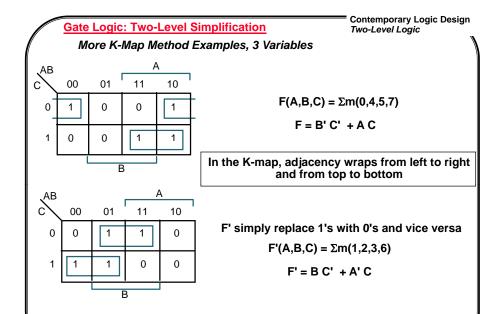

# More K-Map Method Examples, 3 Variables

$$\mathsf{F}(\mathsf{A},\mathsf{B},\mathsf{C}) = \Sigma \mathsf{m}(0,4,5,7)$$

F=

#

F' simply replace 1's with 0's and vice versa

$$F'(A,B,C) = \Sigma m(1,2,3,6)$$

F' =

© R.H. Katz Transparency No. 2-45

Compare with the method of using DeMorgan's Theorem and Boolean Algebra to reduce the complement!

© R.H. Katz Transparency No. 2-46

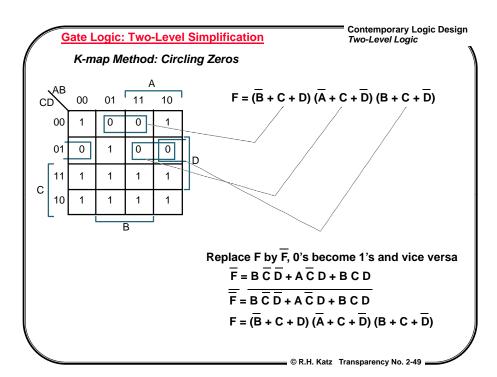

## **Gate Logic: Two-Level Simplification**

Contemporary Logic Design

Two-Level Logic

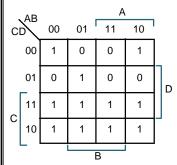

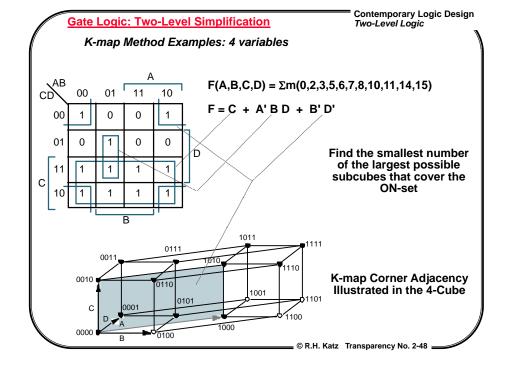

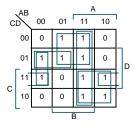

#### K-map Method Examples: 4 variables

$F(A,B,C,D) = \Sigma m(0,2,3,5,6,7,8,10,11,14,15)$

F =

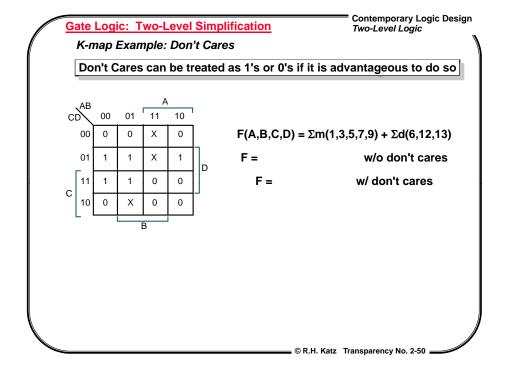

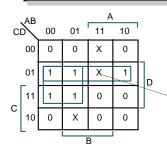

## Gate Logic: Two-Level Simplification

Contemporary Logic Design Two-Level Logic

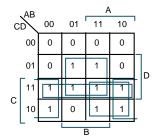

K-map Example: Don't Cares

Don't Cares can be treated as 1's or 0's if it is advantageous to do so

In PoS form: F = D(A' + C')

Same answer as above,

but fewer literals

$F(A,B,C,D) = \Sigma m(1,3,5,7,9) + \Sigma d(6,12,13)$

F = A'D + B' C' D w/o don't cares

F = C' D + A' D w/ don't cares

By treating this DC as a "1", a 2-cube can be formed rather than one 0-cube

■ © R.H. Katz Transparency No. 2-51

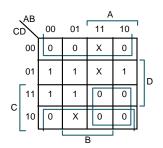

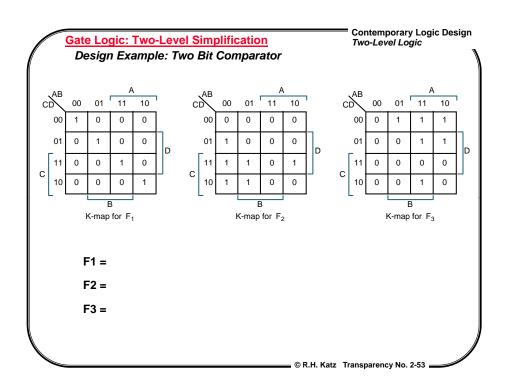

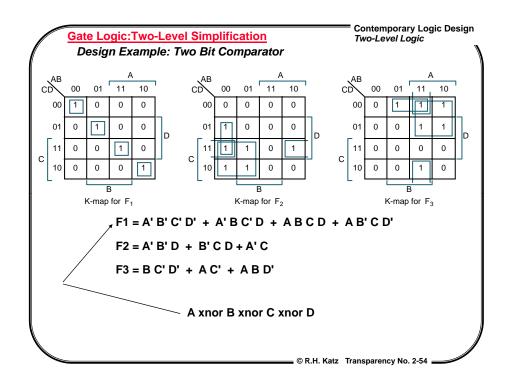

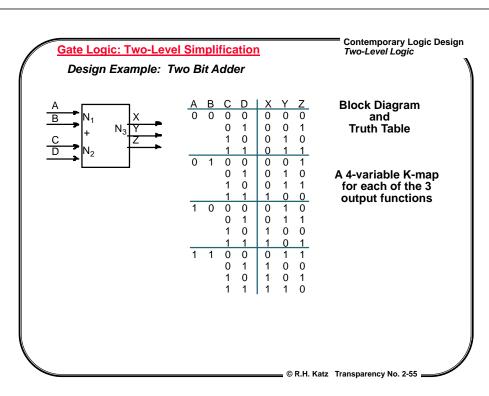

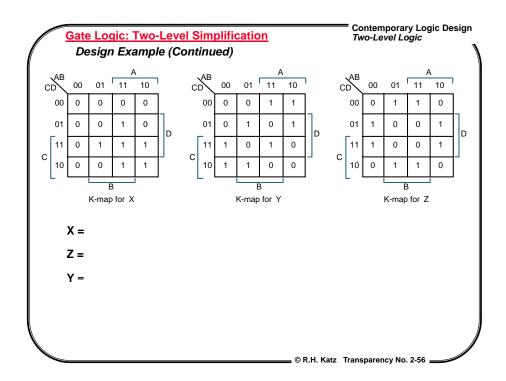

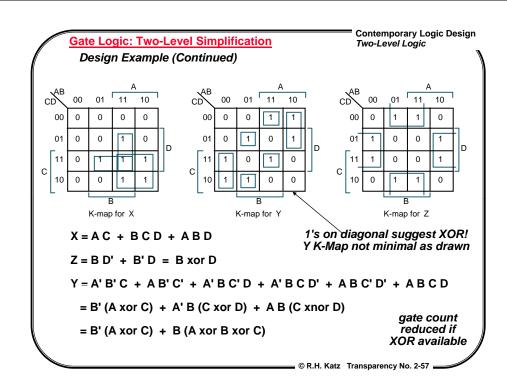

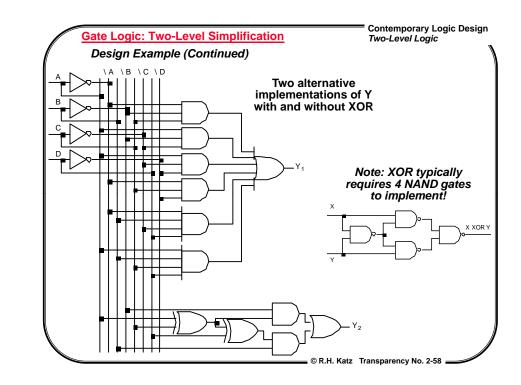

# **Gate Logic: Two-Level Simplification**

Design Example: Two Bit Comparator

| Α | В | С                                    | D                                                                  | F₁                              | $F_2$       | $F_3$                                                         |

|---|---|--------------------------------------|--------------------------------------------------------------------|---------------------------------|-------------|---------------------------------------------------------------|

| 0 | 0 | 0<br>1<br>1<br>0<br>0<br>1<br>1      | 0                                                                  | 1                               | 0           | 0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0 |

|   |   | 0                                    | 1                                                                  | 0                               | 1           | 0                                                             |

|   |   | 1                                    | 0                                                                  | 0                               | 1           | 0                                                             |

|   |   | 1                                    | 1                                                                  | 0                               | 1           | 0                                                             |

| 0 | 1 | 0                                    | 0                                                                  | 1<br>0<br>0<br>0<br>1<br>0      | 0           | 1                                                             |

|   |   | 0                                    | 1                                                                  | 1                               | 0           | 0                                                             |

|   |   | 1                                    | 0                                                                  | 0                               | 1           | 0                                                             |

|   |   | 1                                    | 1                                                                  | 0                               | 1           | 0                                                             |

| 1 | 0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 |                                 | 0           | 1                                                             |

|   |   | 0                                    | 1                                                                  | 0                               | 0           | 1                                                             |

|   |   | 1                                    | 0                                                                  | 1                               | 0           | 0                                                             |

|   |   | 1                                    | 1                                                                  | 0                               | 1_          | 0                                                             |

| 1 | 1 | 0                                    | 0                                                                  | 0<br>0<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>0 | 1                                                             |

|   |   | 0                                    | 1                                                                  | 0                               | 0           | 1                                                             |

|   |   | 1                                    | 0                                                                  | 0                               | 0           | 1                                                             |

|   |   | 1                                    | 1                                                                  | 1                               | 0           | 0                                                             |

|   |   |                                      |                                                                    |                                 |             |                                                               |

Contemporary Logic Design

Block Diagram and Truth Table

A 4-Variable K-map for each of the 3 output functions

**Gate Logic: Two Level Simplification**

Contemporary Logic Design

Definition of Terms

*implicant*: single element of the ON-set or any group of elements that can be combined together in a K-map

prime implicant: implicant that cannot be combined with another implicant to eliminate a term

essential prime implicant: if an element of the ON-set is covered by a single prime implicant, it is an essential prime

Objective:

grow implicants into prime implicants

cover the ON-set with as few prime implicants as possible

essential primes participate in ALL possible covers

■ © R.H. Katz Transparency No. 2-6

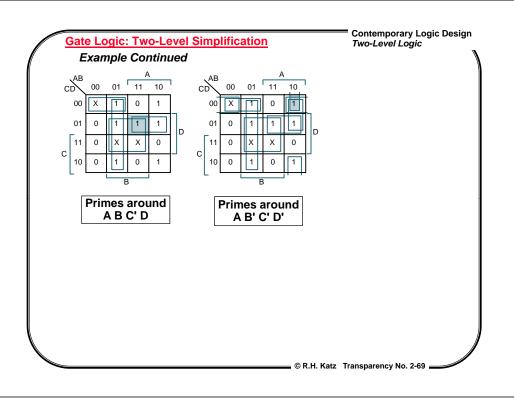

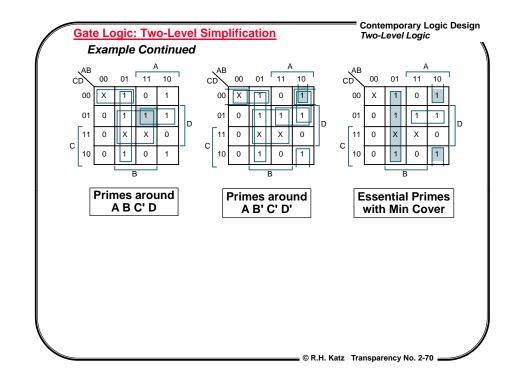

#### **Gate Logic: Two Level Simplication**

Contemporary Logic Design Two-Level Logic

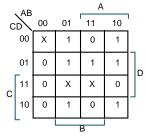

#### Examples to Illustrate Terms

6 Prime Implicants:

A' B' D, B C', A C, A' C' D, A B, B' C D

essential

Minimum cover = B C' + A C + A' B' D

5 Prime Implicants:

B D, A B C', A C D, A' B C, A' C' D

Essential implicants form minimum cover

■ © R.H. Katz Transparency No. 2-62

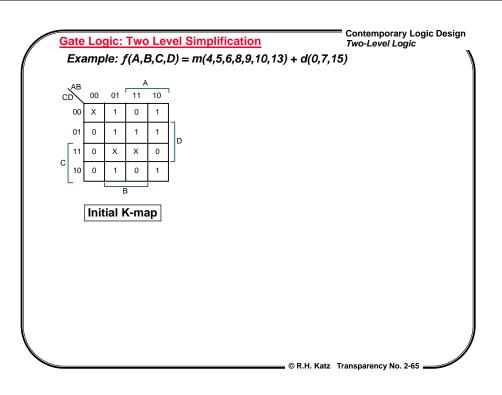

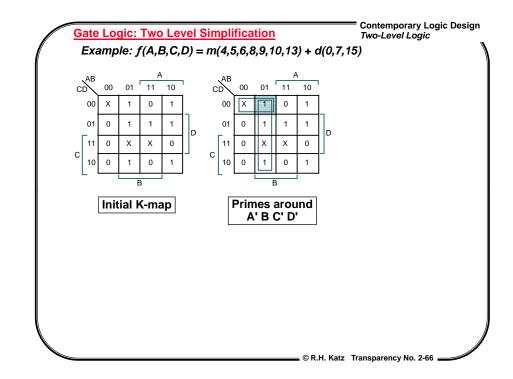

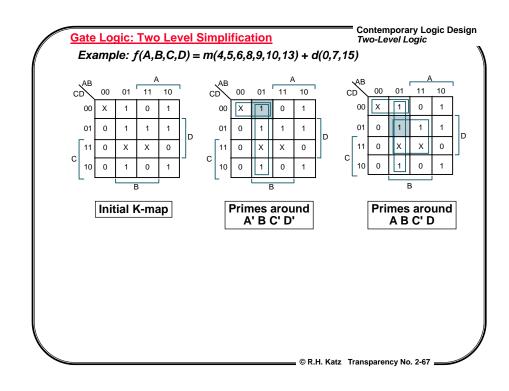

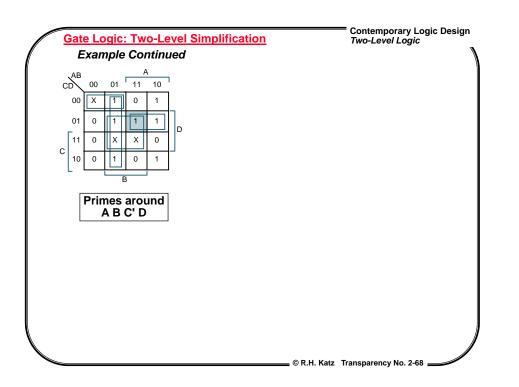

#### Gate Logic: Two Level Simplification

Contemporary Logic Design Two-Level Logic

More Examples

**Prime Implicants:**

B D, C D, A C, B' C essential

Essential primes form the minimum cover

# **Gate Logic: Two-Level Simplification**

Contemporary Logic Design

Two-Level Logic

Algorithm: Minimum Sum of Products Expression from a K-Map

- Step 1: Choose an element of ON-set not already covered by an implicant

- Step 2: Find "maximal" groupings of 1's and X's adjacent to that element. Remember to consider top/bottom row, left/right column, and corner adjacencies. This forms *prime implicants* (always a power of 2 number of elements).

Repeat Steps 1 and 2 to find all prime implicants

- Step 3: Revisit the 1's elements in the K-map. If covered by single prime implicant, it is essential, and participates in final cover. The 1's it covers do not need to be revisited

- Step 4: If there remain 1's not covered by essential prime implicants, then select the smallest number of prime implicants that cover the remaining 1's

#

# Gate Logic: CAD Tools for Simplification

Contemporary Logic Design

Two-Level Logic

Quine-McCluskey Method

Tabular method to systematically find all prime implicants

$f(A,B,C,D) = \Sigma m(4,5,6,8,9,10,13) + \Sigma d(0,7,15)$

Stage 1: Find all prime implicants

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

| Implication Table            |           |            |  |  |

|------------------------------|-----------|------------|--|--|

| Column I                     | Column II | Column III |  |  |

| 0000                         |           |            |  |  |

| 0100<br>1000                 |           |            |  |  |

| 0101<br>0110<br>1001<br>1010 |           |            |  |  |

| 0111<br>1101                 |           |            |  |  |

| 1111                         |           |            |  |  |

© R.H. Katz Transparency No. 2-75

#### Gate Logic: CAD Tools for Simplification

Contemporary Logic Design

Quine-McCluskey Method

Tabular method to systematically find all prime implicants

$f(A,B,C,D) = \Sigma m(4,5,6,8,9,10,13) + \Sigma d(0,7,15)$

Stage 1: Find all prime implicants

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

Step 2: Apply Uniting Theorem—

Compare elements of group w/

N 1's against those with N+1 1's.

Differ by one bit implies adjacent.

Eliminate variable and place in next column.

E.g., 0000 vs. 0100 yields 0-00 0000 vs. 1000 yields -000

When used in a combination, mark with a check. If cannot be combined, mark with a star. These are the prime implicants.

|   | Column I | Column II | Column III |

|---|----------|-----------|------------|

|   | 0000 ✓   | 0- 00     |            |

|   |          | - 000     |            |

|   | 0100 ✓   |           |            |

|   | 1000 ✓   | 010-      |            |

|   |          | 01- 0     |            |

|   | 0101 ✓   | 100-      |            |

|   | 0110 ✓   | 10- 0     |            |

|   | 1001 ✓   |           |            |

|   | 1010 ✓   | 01-1      |            |

|   |          | -101      |            |

|   | 0111 ✓   | 011-      |            |

|   | 1101 ✓   | 1-01      |            |

|   |          | 444       |            |

| ١ | 1111 ✓   | -111      |            |

|   |          | 11-1      |            |

**Implication Table**

Repeat until no further combinations can be made.

#### **Gate Logic: CAD Tools for Simplification**

Contemporary Logic Design Two-Level Logic

**Quine-McCluskey Method**

Tabular method to systematically find all prime implicants

$f(A,B,C,D) = \Sigma m(4,5,6,8,9,10,13) + \Sigma d(0,7,15)$

Stage 1: Find all prime implicants

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

Step 2: Apply Uniting Theorem—

Compare elements of group w/

N 1's against those with N+1 1's.

Differ by one bit implies adjacent.

Eliminate variable and place in

next column.

E.g., 0000 vs. 0100 yields 0-00 0000 vs. 1000 yields -000

When used in a combination, mark with a check. If cannot be combined, mark with a star. These are the prime implicants.

| lm       | ıble                            |            |

|----------|---------------------------------|------------|

| Column I | Column II                       | Column III |

| 0000 ✓   | 0- 00 *<br>- 000 *              | 01 *       |

| 0100 ✓   |                                 | -1-1 *     |

| 1000 ✓   | 010- <b>√</b><br>01- 0 <b>√</b> |            |

| 0101 ✓   | 100- *                          |            |

| 0110 ✓   | 10-0 *                          |            |

| 1001 ✓   |                                 |            |

| 1010 ✓   | 01-1 ✓                          |            |

|          | -101 ✓                          |            |

| 0111 ✓   | 011- ✓                          |            |

| 1101 ✓   | 1-01 *                          |            |

| 1111 ✓   | -111 <b>√</b><br>11-1 <b>√</b>  |            |

Repeat until no further combinations can be made.

© R.H. Katz Transparency No. 2-77

© R.H. Katz Transparency No. 2-79

Contemporary Logic Design

Two-Level Logic

### Gate Logic: CAD Tools for Simplification

Contemporary Logic Design Two-Level Logic

# Quine-McCluskey Method Continued

#### Prime Implicants:

■ © R.H. Katz Transparency No. 2-78

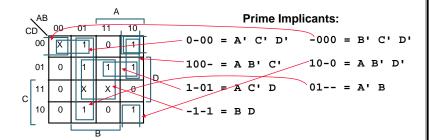

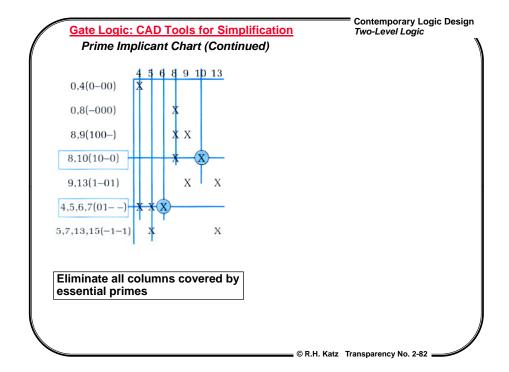

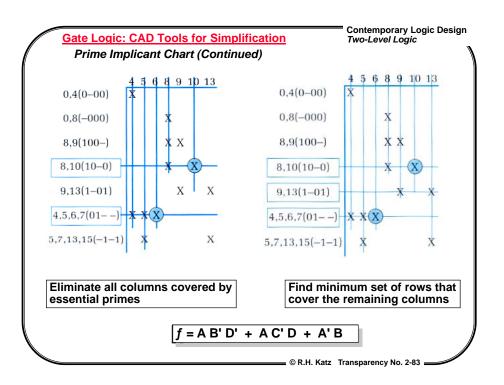

# Gate Logic: CAD Tools for Simplification

**Quine-McCluskey Method Continued**

Stage 2: find smallest set of prime implicants that cover the ON-set recall that essential prime implicants must be in all covers another tabular method– the prime implicant chart

Gate Logic: CAD Tools for Simplification

Prime Implicant Chart

rows = prime implicants

columns = ON-set elements

place an "X" if ON-set element is

covered by the prime implicant

Contemporary Logic Design

Gate Logic: CAD Tools for Simplification

Problem with Quine-McCluskey: the number of prime implicants grows rapidly with the number of inputs

upper bound: 3 <sup>n</sup>/n, where n is the number of inputs

finding a minimum cover is NP-complete, i.e., a computational expensive process not likely to yield to any efficient algorithm

Espresso: trades solution speed for minimality of answer

don't generate all prime implicants (Quine-McCluskey Stage 1)

judiciously select a subset of primes that still covers the ON-set

operates in a fashion not unlike a human finding primes in a K-map

Contemporary Logic Design

Two-Level Logic

#### Gate Logic: CAD Tools for Simplification

Contemporary Logic Design Two-Level Logic

Espresso Method: Overview

Expands implicants to their maximum size

Implicants covered by an expanded implicant are removed from

further consideration

Quality of result depends on order of implicant expansion

Heuristic methods used to determine order

Step is called EXPAND

- Irredundant cover (i.e., no proper subset is also a cover) is extracted from the expanded primes

Just like the Quine-McCluskey Prime Implicant Chart

Step is called IRREDUNDANT COVER

- 3. Solution usually pretty good, but sometimes can be improved Might exist another cover with fewer terms or fewer literals Shrink prime implicants to smallest size that still covers ON-set Step is called REDUCE

- 4. Repeat sequence REDUCE/EXPAND/IRREDUNDANT COVER to find alternative prime implicants Keep doing this as long as new covers improve on last solution

- 5. A number of optimizations are tried, e.g., identify and remove essential primes early in the process

© R.H. Katz Transparency No. 2-85

#### **Gate Logic: CAD Tools for Simplification**

Espresso Inputs and Outputs

f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

-- ABCD don't care

-- end of list

#### **Espresso Input**

1111

.e

#### .i 4 -- # inputs .0 1 -- # outputs .ilb a b c d -- input names .ob f -- output name .p 10 -- number of product terms 0100 1 -- A'BC'D' 0101 -- A'BC'D 0110 -- A'BCD' 1000 -- AB'C'D' 1001 -- AB'C'D 1010 -- AB'CD' 1101 -- ABC'D 0000 -- A'B'C'D' don't care 0111 -- A'BCD don't care

#### Espresso Output

Contemporary Logic Design

Two-Level Logic

■ © R.H. Katz Transparency No. 2-86

#### Gate Logic: CAD Tools for Simplification

Contemporary Logic Design

Two-Level Logic

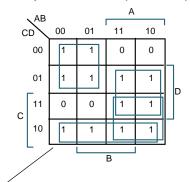

#### Espresso: Why Iterate on Reduce, Irredundant Cover, Expand?

Initial Set of Primes found by Steps1 and 2 of the Espresso Method

4 primes, irredundant cover, but not a minimal cover!

Result of REDUCE: Shrink primes while still covering the ON-set

Choice of order in which to perform shrink is important

**Gate Logic: CAD Tools for Simplification**

Contemporary Logic Design Two-Level Logic

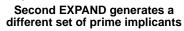

# Espresso Iteration (Continued)

IRREDUNDANT COVER found by final step of espresso

Only three prime implicants!

© R.H. Katz Transparency No. 2-87

## **Two-Level Logic: Summary**

Contemporary Logic Design Two-Level Logic

Primitive logic building blocks

INVERTER, AND, OR, NAND, NOR, XOR, XNOR

**Canonical Forms**

**Sum of Products, Products of Sums**

Incompletely specified functions/don't cares

Logic Minimization

Goal: two-level logic realizations with fewest gates and fewest number of gate inputs

Obtained via Laws and Theorems of Boolean Algebra

or Boolean Cubes and the Uniting Theorem

or K-map Methods up to 6 variables

or Quine-McCluskey Algorithm

or Espresso CAD Tool